Che il mondo dei transistor, dei chip e dei processori sia destinato a cambiare drasticamente nel giro di qualche anno è ormai un fatto assodato. La Legge di Moore, che per 50 anni ha dettato i ritmi di sviluppo del settore, è ormai avviata sul viale del tramonto e i produttori di CPU sono da tempo alla ricerca di una o più possibili soluzioni per evitare di farsi trovare impreparati. Gran parte delle ipotesi di studio e delle proposte sono contenute nell'International Technology Roadmap for Semiconductors (ITRS), una serie di documenti prodotto annualmente da un gruppo di esperti nel campo dei semiconduttori.

È tra le pagine di questo report che, solitamente, si scoprono le tendenze del settore e si può sapere "quello che sarà" dei transistor e dei chip del futuro. Le analisi condotte dagli esperti, infatti, sono sempre piuttosto precise e riescono a prevedere, anche con un buon margine di tempo, quelli che saranno gli sviluppi futuri nel mondo dei processori. Allo stesso tempo, però, anche i singoli produttori (o loro consorzi) portano avanti ricerche per realizzare chip sempre più potenti ed efficienti (anche da un punto di vista energetico) nonostante la Legge di Moore.

I problemi della Legge di Moore

Quando si parla di "Legge di Moore" ci si riferisce a una teoria avanzata nell'aprile del 1965 da Gordon E. Moore, allora direttore del Laboratorio di Sviluppo e Ricerca della Fairchild Semiconductor. Lo studioso statunitense, analizzando il trend di crescita degli anni precedenti, aveva teorizzato che il numero di transistor presenti all'interno di un singolo chip sarebbe raddoppiato ogni 18 mesi circa. Una previsione valida ancora oggi, nonostante siano passati ben 50 anni dalla sua enunciazione.

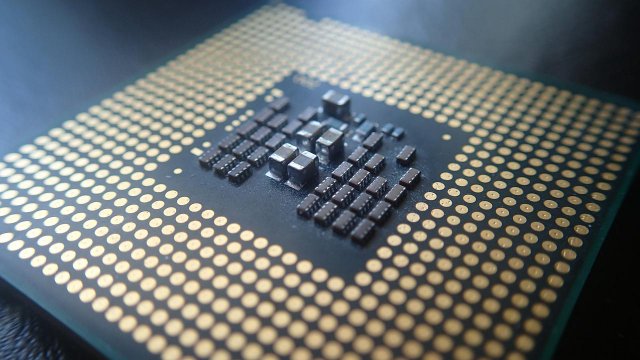

Merito dei progressi registrati nel campo della miniaturizzazione, che ha permesso di "strizzare" i transistor a tal punto da riuscire a stamparne uno ogni 10 nanometri circa (tanto per essere più chiari, un nanometro equivale a un miliardesimo di metro). Arrivati a questo punto, però, è sempre più difficile riuscire a miniaturizzare le componenti necessarie al funzionamento di un chip (non solo i transistor, ma anche i sistemi di dissipazione del calore, i collegamenti tra le varie componenti e così via) e, nonostante sembri che i maggiori produttori del settore (i vari Samsung, Intel, IBM e i marchi cinesi) si stiano preparando per il processo produttivo a 7 nanometri, appare chiaro che i giorni della Legge di Moore sono ormai contati.

Le previsioni dell'International Technology Roadmap for Semiconductor

Nel suo ultimo rapporto, l'ITRS individua due problematiche maggiori per lo sviluppo del settore dei chip. Prima di tutto, dal 2021 in poi non sarà più economicamente vantaggioso continuare a rimpicciolire i transistor; e, alla luce anche di questa valutazione, i produttori dovranno trovare una strada per far sì che la Legge di Moore continui a essere valida nonostante i transistor abbiano raggiunto (o quasi) il loro limite fisico.

Come dimostrano diverse analisi empiriche, infatti, continuare a rimpicciolire i transistor dai 22 nanometri in giù implica costi produttivi sempre maggiori. Oltre un certo limite, potrebbe addirittura diventare antieconomico, con i costi di produzione superiori agli eventuali profitti. Ciò ha un impatto immediato anche per quanto riguarda la Legge di Moore: se i produttori non sono economicamente incentivati a proseguire nella miniaturizzazione, riuscire a raddoppiare il numero di transistor ogni anno e mezzo diverrà impossibile.

L'ITRS, ovviamente, avanza anche alcune ipotesi sulle possibili strade da percorrere per riuscire a uscire da questa sorta di impasse. E, secondo gli esperti internazionali, la strada più veloce è quella che porta verso? l'alto.

Chip verticali

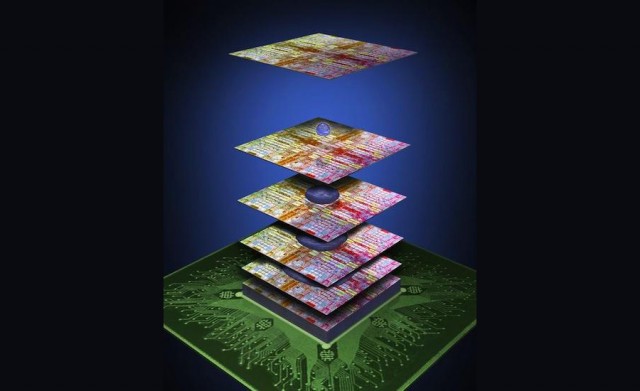

I chip presenti all'interno dei nostri PC, smartphone e altri dispositivi informatici sono basati su un'architettura bidimensionale. I circuiti elettrici alla base dei transistor sono stampati su fogli di silicio caratterizzati da un'estensione "piana". Questa architettura, che allo stato attuale dei fatti rappresenta una limitazione per lo sviluppo del settore dei semiconduttori, potrebbe essere ben presto messa da parte. Secondo gli esperti ITRS i transistor del futuro saranno basati su un design "Gate-all-around" (letteralmente "Porte tutte attorno"), che consentirà collegamenti anche sulla terza dimensione. I chip, dunque, cresceranno in altezza, come fossero dei grattacieli, permettendo di accrescere il numero di transistor ospitabili all'interno della stessa superficie.

Anche questa architettura, però, non è scevra di problematiche. Entro il 2024, infatti, riuscire a dissipare il calore di queste strutture tridimensionali diventerà molto complesso, se non impossibile. In questo caso, l'unica soluzione percorribile sarà quella di ripensare e riprogettare completamente i chip, prevedendo sistemi di dissipazione del calore più "invasivi" e, al tempo stesso, incisivi. Solo in questo modo la Legge di Moore potrà sopravvivere ancora per qualche decennio.

I nanofogli di IBM e Samsung

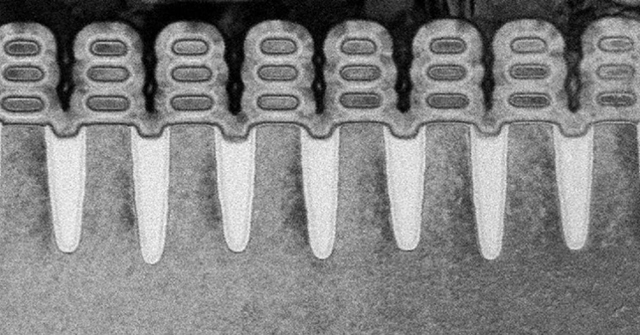

Un altro, possibile, giubbotto di salvataggio per la Legge di Moore è quello che i tecnici IBM e Samsung starebbero confezionando sotto forma di nanofogli (nanosheeet in inglese). Questa soluzione prevede l'utilizzo di un sistema di produzione a 5 nanometri, capace di quadruplicare il numero di transistor oggi presenti all'interno di un chip, migliorando le prestazioni e, al tempo stesso, riducendone il consumo elettrico.

La miniaturizzazione è stata resa possibile grazie a una sostanziale modifica delle porte (o gate) dei transistor, che consentono i collegamenti con le altre componenti del chip e assicurano che la corrente possa scorrere da un capo all'altro del dispositivo. I gate dei nanosheet "circondano" i canali di comunicazione utilizzati all'interno del chip, garantendo così una migliore efficienza nello scorrimento degli elettroni e, dunque, consumi energetici ridotti.

Nuove architetture

Negli ultimi anni, per aggirare i limiti della Legge di Moore (ovvero l'impossibilità tecnologica di continuare ad aumentare il numero di transistor presenti in un singolo processore), sono state ipotizzate e successivamente realizzate nuove architetture informatiche che consentono di moltiplicare la potenza di calcolo dei processori. In particolare, due di queste architetture sembrano essere le più promettenti, sia sul fronte delle performance sia su quello della fattibilità: i chip quantistici e i chip neuromorfici.

I primi hanno il potenziale per essere migliaia di volte (se non milioni di volte) più performanti dei normali chip in silicio e sono in avanzata fase di sviluppo. Tra le altre, Google, IBM e Intel sembrano essere le aziende che più credono (e investono) su questa tecnologia: Big G, ad esempio, ha acquistato la startup D-Wave e realizzato prototipi di computer quantistici con una potenza che, attualmente, arriva ai 50 qubit (il qubit è l'equivalente quantistico del bit ed è utilizzato, al momento, come "unità di misura" per la potenza di calcolo dei processori quantistici); Intel, pur essendo una delle ultime a essersi aggregata alla "carovana" ha raggiunto già risultati eccellenti, presentando al CES 2018 un chip quantistico a 49 qubit.

I chip neuromorfici, come lascia intendere anche il nome, sono processori di nuova generazione che "imitano" il funzionamento del cervello umano per moltiplicare le loro capacità di calcolo ed elaborazione dei dati. Migliaia di volte più efficienti rispetto agli attuali chip in silicio, le CPU neuromorfiche eccellono, in particolare, nel riconoscimento dei pattern (pattern recognition in inglese), branca particolarmente importante nell'ambito dell'intelligenza artificiale e del machine learning.

Calcolo ottimizzato

Una strada alternativa alle precedenti che non punta a sviluppare nuove CPU con strutture innovative ma tenta piuttosto di sfruttare al massimo quello che i chip attuali già hanno da offrire, è quella del cosiddetto calcolo ottimizzato. Questo approccio prevede la progettazione e realizzazione di "normali" chip al silicio, specializzati però per svolgere un particolare tipo di calcolo. Si va dai processori FPGA (sui quali sta investendo Microsoft) ai chip progettati specificatamente per l'intelligenza artificiale (come il SoC Kirin 970 di Huawei e l'A11 di Apple) o per compiti di deep learning (vedi gli investimenti di Google). Ciò consente di migliorare notevolmente le performance dei processori basati su tecnologie già disponibili, senza che i limiti della Legge di Moore rappresentino un problema immediato.